日前,台積電 TSMC 的研發副總經理余振華表示,公司的 3D Fabric 先進封裝技術平台已建立完成並率先進入新階段,由異質系統整合進入到「系統微縮」(System Scaling) 階段,進一步追求效能、功耗及更緊密的尺寸,步向類似 SoC 的發展。

台積電研發副總余振華表示,台積電的 3D Fabric 平台已建立好,且陸續量產、率先進入新階段,已從異質系統整合到現在類似 SoC 微縮的系統微縮 (system scaling),追求更高的系統效能、更低耗能,及更緊密的尺寸。同時又指出,未來台積電在異質整合上,主要專注的兩個方向:一為晶片間導線整合密度的強化,二為封裝尺寸大小持續提升,以提供更高的運算效能、更精密的耗能表現,及在同樣的體積內加入更多異質功能。

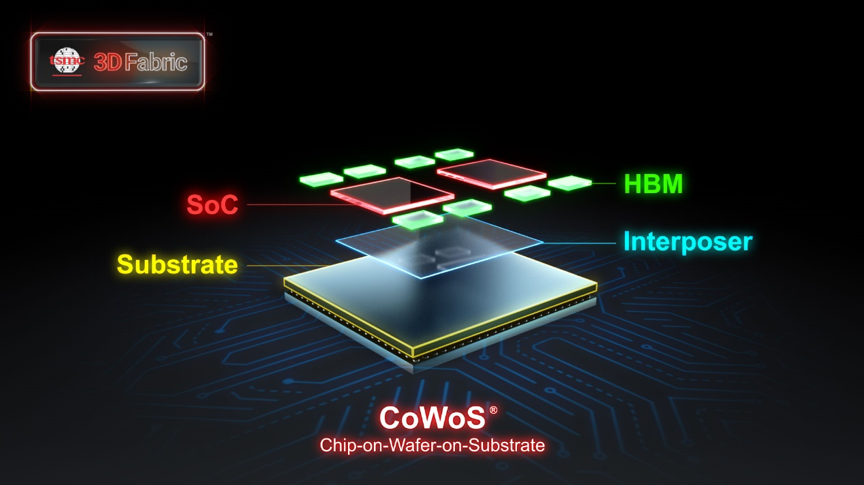

- CoWoS with Multi-Die, HBM and Interposer

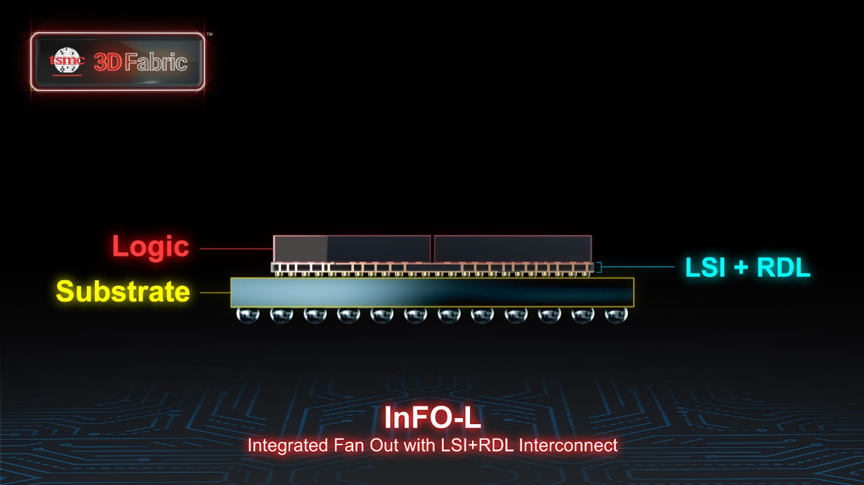

- InFO-L with Multi-Die, LSI Interconnect and RDL

3DFabric 可為 HPC、智慧型手機和物聯網邊緣裝置提供了外形設計的優勢,允許以更密集的 2D、2.5D 或 3D 互連配置,將運算核心與異構微型晶片或小晶片整合在一起,從而大幅縮小了元件和主機板的尺寸,並實現具有更強功能的尖端工業設計。