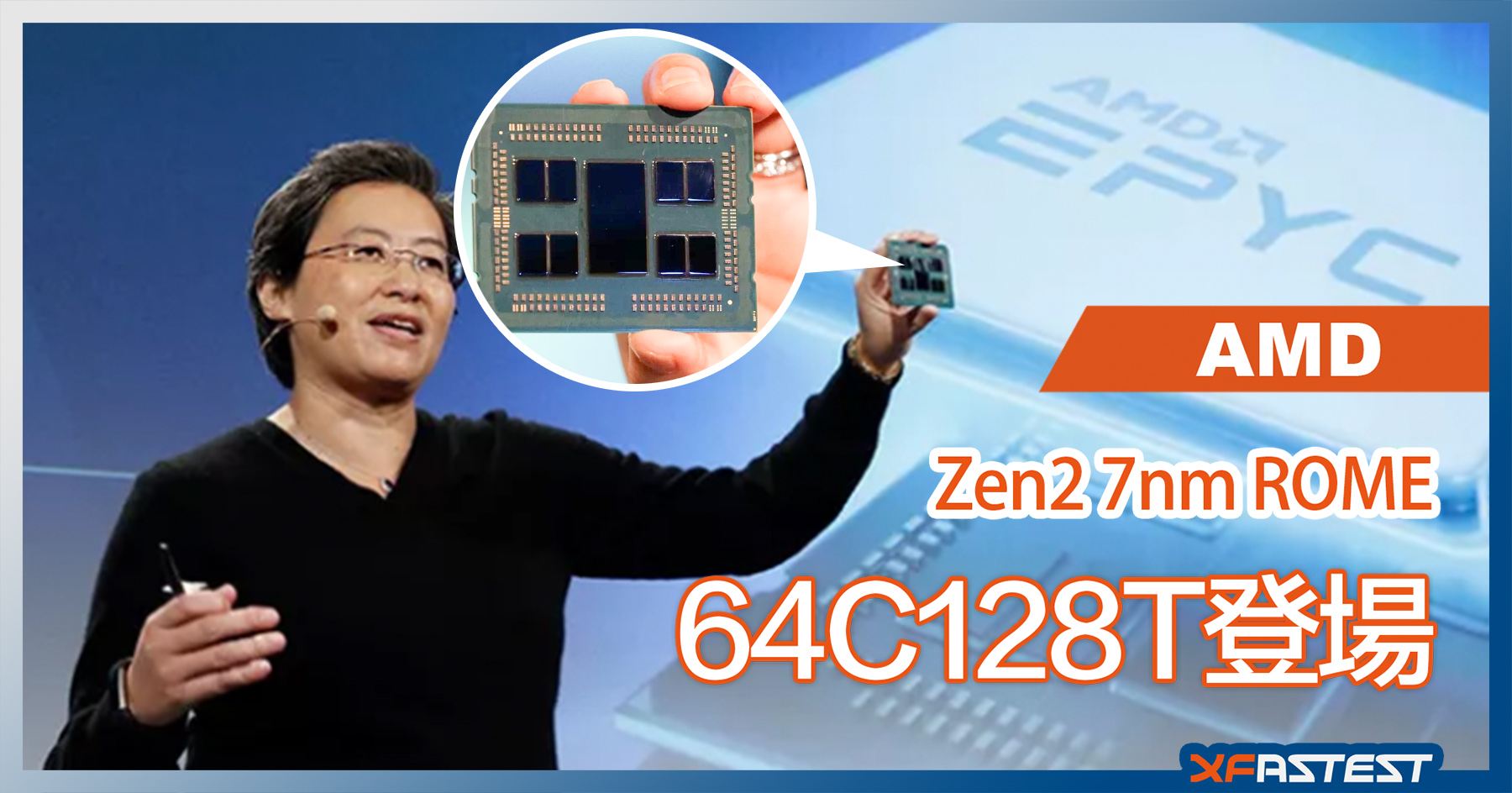

在今天凌晨的新地平線會議上,AMD正式宣布了全球第一個7nm數據中心服務器以及7nm數據中心顯卡,會議內容很多,先來看看CPU方面的。這次宣布的是代號ROME的新一代 EPYC服務器處理器,使用了台積電7nm工藝以及Zen 2架構,從之前最多32核64線程提升到了64核128線程,同時支持PCIe 4.0,目前新一代EPYC已經出樣,並獲得亞馬遜等廠商的認可, 後續的Zen 3架構已經在路上,Zen 4架構則在開發中。

首先來看官方PPT中對Zen 2架構及7nm工藝的具體介紹:

AMD路線圖中,Zen及Zen +架構分別使用14nm,12nm工藝,已經上市了,7nm Zen 2架構處理器已經出樣,Zen 3架構將使用7nm +工藝,也就是7nm EUV工藝,目前進展正常,按部就班進行中。

7納米工藝的優點

對外界來說,為7nm工藝是AMD近年來首次在制程工藝上領先Intel處理器,對AMD自己來說,為7nm工藝帶來的好處主要是技術方面的,晶體管密度提升一倍,功耗降低50% ,同功耗下性能提升25% – 在隔壁的7nm Vega上,AMD提到的數據是降低50%能耗,性能提升30%

與競爭對手的工藝對比

Zen 2架構改進一覽

除了7nm工藝,代號ROME的EPYC處理器也升級到了Zen 2架構,AMD表示它在執行單元,安全性以及模塊化設計,生產性方面也做了改進。

Zen 2架構核心改進

Zen 2架構在前端,浮點,緩存等方面都做了改進,改善了執行單元,加倍了浮點位寬到256bit,加倍了核心密度,降低了一半的操作功耗等等。

安全性增強

ROME處理器主打數據中心市場,安全性也非常重要,Zen 2架構在內存加密,軟件以及幽靈漏洞方面都做了加強。

Zen 2架構的多芯片封裝

Zen 2架構另一個變化就是多晶片封裝了,從首圖可以看到Zen 2內部的模塊跟Zen一代的不同了,因為AMD在Zen 2設計的是I / O核心外置+ CPU核心的結構, 而且使用的是不同的工藝,簡單來說就是Zen 2處理器中有一個14nm工藝的I / O核心(包括DDR記憶體控制器),周圍排布的則是7nm Zen 2核心。

對於這種設計,AMD表示它的優點很多,可以提高良率,具備更高的可配置性,或許這就是Zen 2處理器能夠實現64核128線程的關鍵了,畢竟按照傳統思路做下去,64+核心帶來的難度及良率考驗都是超常規的。

對於這種架構,最大的擔心還是內存延遲之類的,不過現在提這個還太早,這個問題等有了詳細資料再來討論。

Zen 2架構總結

AMD Zen架構處理器路線圖