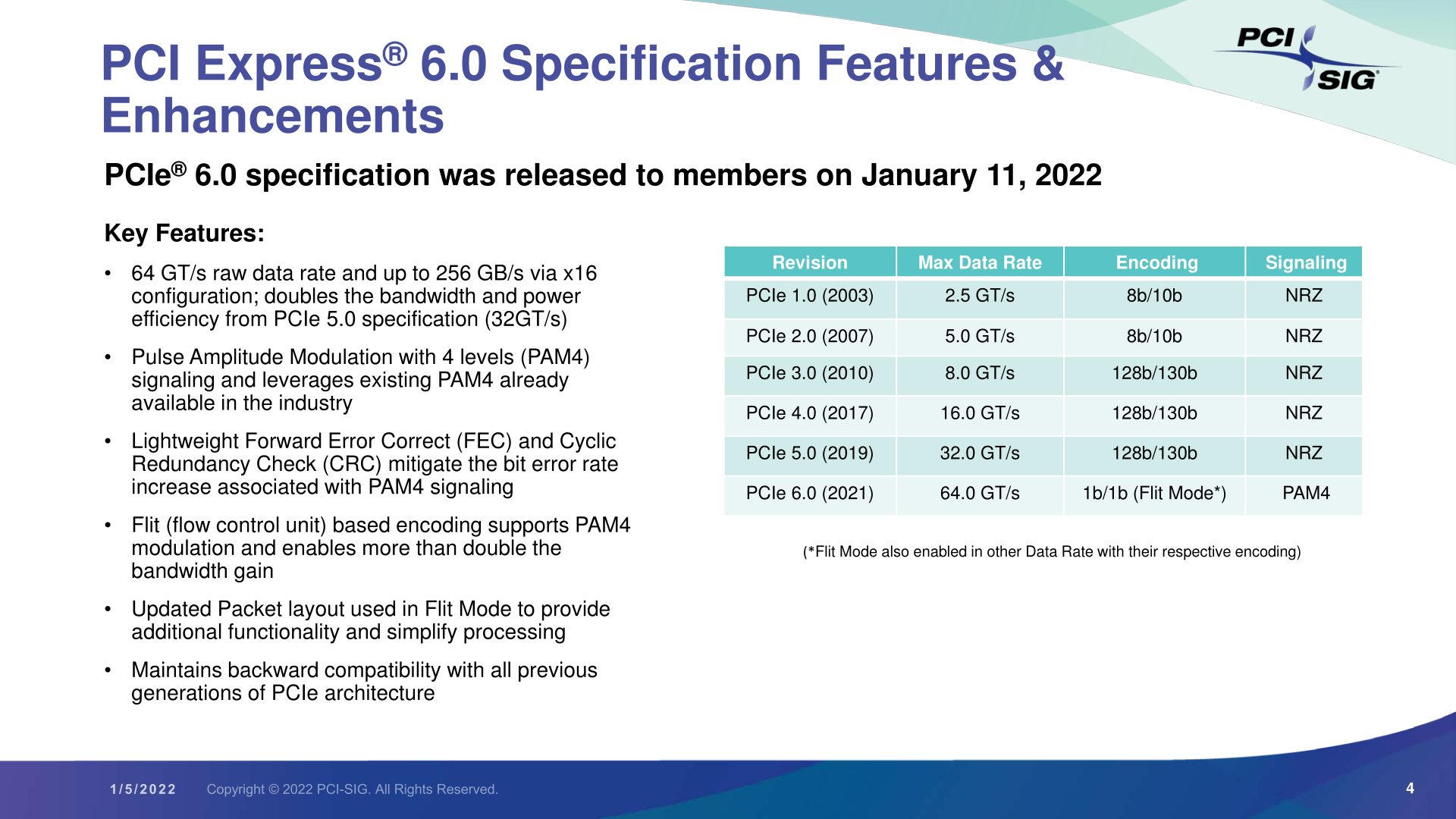

這個星期,PCI-SIG 組織正式發佈了 PCI-E 6.0 標準 v1.0。一如以往,頻寬速度繼續倍數上升,x16 通道下可達到 128GB/s (單向),而因為 PCIe 技術允許數據全雙工雙向傳輸,因此雙向總吞吐量為 256GB/s。按照其計劃,在此標準公佈的 12 – 18 個月後,才會有商用例子出現,即大約到了 2023 年才會見到,主要會在伺服器平台上率先採用。

PCI-E 6.0 被認為是 PCIe 面世近 20 年以來變化最大的一次。主要來說,PCI-E 4.0 / 5.0 都是對 PCI-E 3.0 作出微小的變動而來,如依舊採用基於 NRZ (Non-Return-to-Zero) 的 128b / 130b 編碼。而 PCI-E 6.0 則改用 PAM4 脈沖調幅信令 1b / 1b 編碼,單個信號就有能四種編碼狀態 (00/01/10/11),允許承載最高 30GHz 頻率。不過,由於 PAM4 信號比 NRZ 脆弱,所以又加上了 FEC 前向糾錯機制,糾正鏈路中的信號錯誤,確保數據完整性。

除了 PAM4 和 FEC 之外,PCI-E 6.0 的還加入一項主要技術,就是在邏輯層使用 FLIT (流量控制單元) 編碼。其實 PAM4、FLIT 都不算是新技術,在 200G+ 的超高速 Ethernet 上早已應用,而當中 PAM4 沒有大規模使用的原因是在於物理層的成本太高。

另外,PCI-E 6.0 同樣地保持了對向下兼容的能力。