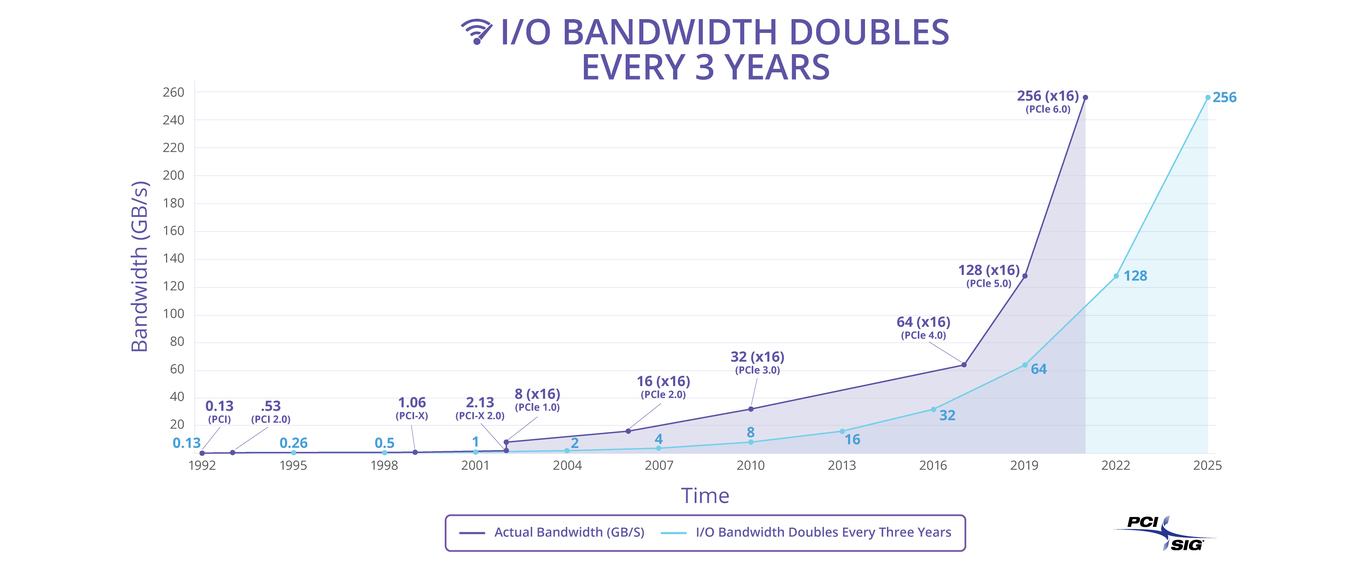

受到疫情影響,今年的 PCI-SIG 年度大會採用的是線上的方式舉行,在會議中 PCI-SIG 的總裁 Al Yanes 在介紹了 PCI-E 規範的最新發展。畢竟 PCI-SIG 在先前足足用上 7 年時間才完成 PCI-E 4.0 標準,這樣的時間實在是拖得有點久,為了不再重蹈覆轍,PCI-SIG 表示 PCI-E 5.0 及以後的版本將會加快規格更新頻率。

雖然目前縱使是 PCI-E 4.0 的部分都還尚未普及,就連 Intel 在第十代 Comet Lake-S 的 CPU 上都還未實裝 PCI-E 4.0 的功能,而 PCI-E 5.0 的最終版本規範也已經在去年 (2019) 中的時候敲定,目前幾間 IC 設計大廠也已經在著手於 PCI-E 5.0 的相關產品與解決方案。

如果對於 PCI-E 相關技術規範有研究的讀者應該都知道,PCI-E 在從 2.0 跨至 3.0 的規範時代中,將編碼機制自 8b/10b 改變為 128b/130b,而 PCI-E 5.0 的部分則也是使用 128b/130b,唯獨編碼規格採用了基頻不歸零 (NRZ) 調變架構。

而 PCI-E 6.0 將預計照樣維持 128b/130b,但在編碼規格上將更改為四階脈衝振幅調變 (PAM4),此外也加入了 RS-FEC 糾錯機制,傳輸速率將可達 64.0 GT/s,x16 下的頻寬將約為 126.03 GB/s。目前 PAM4 編碼規格已經被廣泛地在許多高速連接介面的草案標準上採用,例如速率可高達單埠 400 GbE 的 IEEE 802.3cd 有線網路標準草案等。

當然,PCI-E 6.0 也一併將會帶來在 PCB Layout 等方面更棘手的影響,自 PCI-E 4.0 開始,系統廠就已經開始面臨到在傳統 FR4 材質的板卡上信號不足以應付足夠長的走線的問題,根據 EETaiwan 的相關報導,PCI-E 4.0 的高速訊號在沒有穿過任何連接器的情況下,走不到約 12 吋的長度就會逐漸消失,要解決這類的問題將必須採用配置信號中繼器 (Retimer / Redriver) 或更換更貴更高級的 PCB 材質等措施。

PCI-E 6.0 將採用上更加複雜的 PAM4 與 RS-FEC 技術,屆時這樣的標準將會讓 PCB Layout 面臨更高的設計難度與成本考量,畢竟對於普通的用戶或玩家而言,PCI-E 3.0 現階段提供的頻寬就真的已經是相當充足,筆者個人認為縱使明年度 (2021 年) PCI-E 6.0 的規範正式敲定後,估計就算是 PCI-E 5.0 在普通消費等級的產品上,可能都還是需要一段時間後才有機會被廣泛採用,就如同現今的 10 GbE 有線網路一樣。

資料來源 : hardwareluxx、EETaiwan、EETaiwan